Resumen generado por IA

El Future Trends Forum de Semiconductores ha centrado su análisis en el advanced packaging y la integración heterogénea, aspectos clave para la eficiencia energética, escalabilidad y competitividad futura de la industria. Expertos destacan que el próximo salto tecnológico no solo depende de la miniaturización, sino de cómo se conectan y empaquetan los chips. La integración heterogénea permite combinar chips especializados en un mismo encapsulado, reduciendo distancias físicas, el consumo energético y mejorando el ancho de banda, lo que es crucial para aplicaciones como la inteligencia artificial que demandan gran transferencia de datos.

Este nuevo paradigma transforma el chip monolítico en un sistema modular de chiplets, optimizando la fabricación y costes, y superando limitaciones físicas. Además, se están explorando substratos avanzados de vidrio que mejoran la estabilidad y eficiencia energética, y técnicas aditivas para interconexiones más densas y precisas. La integración heterogénea no solo optimiza rendimiento y coste, sino que también impulsa la convergencia tecnológica con fotónica, sensores y materiales compuestos. En este contexto, Europa tiene una oportunidad estratégica para liderar si desarrolla un ecosistema propio con talento e infraestructura especializada. En definitiva, el futuro de los semiconductores reside en la arquitectura del sistema, donde el packaging avanzado es la palanca para sostener el crecimiento tecnológico y económico global.

Advanced Packaging e integración heterogénea: cómo los chiplets redefinen eficiencia, coste y escalabilidad en la era de la IA.

La serie de artículos sobre el Future Trends Forum de Semiconductores avanza hacia uno de los debates más estratégicos para la industria: el advanced packaging y la integración heterogénea. Tras analizar geopolítica y cadena de valor, aplicaciones tractoras y fotónica, el foco se sitúa ahora en el corazón arquitectónico del chip. Aquí se decide la eficiencia energética, la escalabilidad y la competitividad futura.

La conclusión de los expertos del foro es clara: el salto de la próxima década se juega en cómo integramos. La miniaturización continúa, aunque el verdadero diferencial emerge en la forma de conectar, empaquetar y combinar tecnologías.

Este artículo se basa en las intervenciones de tres expertos internacionales que participaron en la sesión dedicada a Advanced Packaging and Heterogeneous Integration.

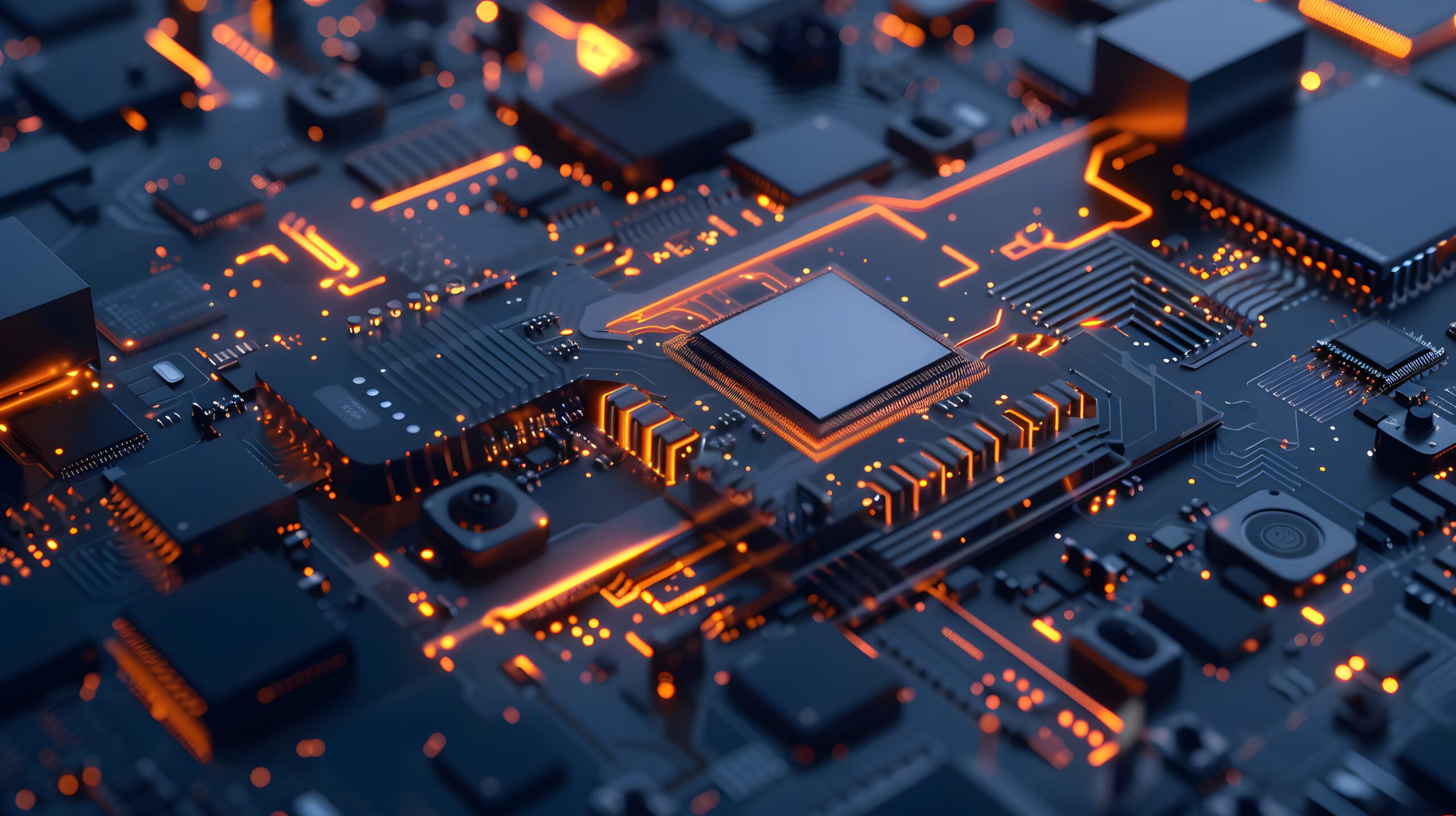

Un nuevo paradigma: integrar con densidad y eficiencia

Muhannad Bakir, director del 3D Systems Packaging Research Center en Georgia Tech (EE. UU.), definió la integración heterogénea como una forma avanzada de empaquetado capaz de integrar chips con distintas funciones a densidades muy elevadas y con bajo consumo energético.

Durante décadas, los sistemas electrónicos se construyeron empaquetando cada chip por separado: CPU en un encapsulado, memoria en otro, conectados a través de la placa base. Esa distancia, de varios centímetros o pulgadas, penaliza energía y ancho de banda. Las interconexiones eléctricas pierden eficiencia cuando la señal recorre trayectos largos.

La solución consiste en acercar físicamente los chips. Reducir distancia reduce energía. Aumenta el ancho de banda. Mejora la densidad de interconexión.

Durante décadas, el diseño de sistemas electrónicos priorizó la lógica y la miniaturización del transistor. Sin embargo, a medida que aumentaba la complejidad, el verdadero coste comenzó a desplazarse: ya no estaba solo en el cálculo, sino en el movimiento de los datos.

Como señaló Muhannad Bakir durante la sesión, hace aproximadamente dos décadas un estudio realizado en Estados Unidos sobre el impacto ambiental de los centros de datos ya advertía de un dato revelador: una parte sustancial de la energía total se consume en enviar datos de un componente a otro dentro del sistema.

Ese diagnóstico, que entonces parecía técnico, hoy es estratégico.

Cada milímetro adicional entre chips implica más consumo, mayor latencia y menor densidad de ancho de banda. En la era de la inteligencia artificial, donde millones de operaciones requieren transferencias constantes entre procesadores y memoria, el coste energético del dato en movimiento se convierte en variable crítica de competitividad.

Reducir distancia física ya no es una optimización incremental. Es una decisión estructural que define la viabilidad energética de la próxima generación de infraestructuras digitales. Cada milímetro importa.

Del chip monolítico al sistema modular

La integración heterogénea responde también a una transformación estructural en la tecnología del silicio.

Bakir citó un análisis publicado por el CEO de Samsung en el que se mostraba que, en nodos avanzados como 3 nanómetros, fragmentar un único chip en varias piezas más pequeñas y reconectarlas a nivel de encapsulado puede generar un ahorro cercano al 50 % en coste de silicio.

La razón es estructural: los chips de menor tamaño presentan mejor rendimiento de fabricación (yield) que los diseños monolíticos de gran área. Al mejorar el número de unidades funcionales por oblea, el coste medio por chip desciende de forma significativa.

La explicación es técnica y estratégica a la vez:

- Chips más pequeños ofrecen mejor rendimiento de fabricación (yield).

- La litografía limita el tamaño máximo por retícula.

- La agregación a nivel de paquete permite escalar potencia más allá del límite monolítico.

AMD ha publicado que puede construir CPUs y GPUs más potentes agregando múltiples núcleos en el paquete, superando las restricciones de la integración tradicional .

El chip deja de ser una pieza única. Se convierte en un sistema modular compuesto por chiplets especializados.

Una nueva “crisis del empaquetado”

Bakir introdujo una analogía histórica potente: en los años cincuenta, los circuitos se construían con transistores individuales soldados a mano. A medida que aumentaba la complejidad, el proceso se volvía inviable. A esa situación se la denominó “la tiranía de los números”.

La solución fue el circuito integrado.

Hoy vivimos otra tensión estructural en el empaquetado. La industria vuelve a enfrentarse a límites físicos y económicos. La pregunta abierta es qué innovación transformadora emergerá ahora para redefinir la construcción de sistemas semiconductores.

El muro del ancho de banda en la era de la IA

La inteligencia artificial acelera esta presión arquitectónica.

Jekaterina Viktorova, directora ejecutiva y cofundadora de Syenta (Australia), profundizó en el llamado AI memory bandwidth wall.

El mayor desafío de hardware para la IA se concentra en dos frentes asociados al empaquetado avanzado:

- Densidad de interconexión.

- Capacidad.

El rendimiento de los sistemas de IA depende de la densidad del cableado que conecta procesadores y memoria. Cuando esa densidad resulta insuficiente, aparece el cuello de botella. Se genera ineficiencia energética en los centros de datos.

La conversación ya gira en torno a transistores. Se centra en cómo mover datos de forma eficiente dentro del sistema. La arquitectura interna determina el consumo global.

Integración heterogénea: eficiencia, rendimiento y coste

El concepto de integración heterogénea combina chips con funciones distintas -lógica, memoria, sensores, aceleradores- dentro de un mismo encapsulado de alta densidad.

Cada chiplet se fabrica con el nodo más adecuado para su función:

- Lógica avanzada en nodos punteros.

- Memoria en nodos optimizados.

- Componentes analógicos en tecnologías maduras.

Este enfoque aporta tres ventajas estratégicas:

1. Optimización económica.

Se utiliza cada nodo donde aporta más valor.

2. Mejora de rendimiento.

La proximidad física reduce latencia y consumo.

3. Escalabilidad modular.

Permite actualizar componentes sin rediseñar el sistema completo.

El empaquetado deja de ser un proceso final. Se convierte en elemento arquitectónico central.

Fabricación aditiva y nuevas interconexiones

En la sesión también se abordó la construcción aditiva de interconexiones de cobre de alta resolución. La densidad del cableado interno impacta directamente en el rendimiento energético de los chips de IA.

El desafío se sitúa en fabricar interconexiones más finas, más densas y con mayor precisión.

Aquí confluyen ciencia de materiales, ingeniería de procesos y diseño de sistemas. La frontera entre fabricación y arquitectura se diluye.

Substratos de vidrio y 3D HDI: el cambio de paradigma en la base del sistema

Sung Jin Kim, director de Tecnología (CTO) de Absolics Inc. (EE. UU.), llevó el debate a un nivel aún más estructural: el substrato.

Si la integración heterogénea acerca chips, el siguiente salto consiste en rediseñar la base sobre la que se conectan.

Kim explicó que la integración 3D de alta densidad (3D HDI) exige un nuevo paradigma arquitectónico. Las soluciones actuales en 2.5D resultan insuficientes para las demandas que llegarán antes de 2030: pasos de interconexión por debajo de 10 micras y densidades de integración sin precedentes.

Aquí emerge el vidrio como material estratégico.

Frente a los substratos orgánicos tradicionales, el vidrio ofrece:

- Mayor estabilidad dimensional

- Coeficiente de expansión térmica ajustable

- Mejor compatibilidad con silicio

- Capacidad para integrar componentes pasivos dentro del propio núcleo

Absolics ha desarrollado un substrato de vidrio completamente integrado en el que los componentes pasivos se embeben directamente en el núcleo. El resultado es una reducción drástica del recorrido electrónico: de varios centímetros a apenas cientos de micras.

Menor recorrido implica:

- Menor consumo energético

- Menor generación térmica

- Mayor rendimiento del sistema

El substrato deja de ser un soporte pasivo. Se convierte en parte activa de la arquitectura energética del chip.

Kim subrayó además que el diseño del chiplet, el encapsulado y el sistema deben desarrollarse en paralelo. La cadena de valor se reorganiza alrededor del packaging avanzado.

La arquitectura ya no se define al final del proceso. Se diseña desde el inicio.

Energía: la variable estratégica

La conversación técnica conecta con una variable sistémica: la energía.

Reducir la distancia entre chips reduce pérdidas. Aumentar la densidad de interconexión mejora eficiencia. Integrar funciones en un mismo paquete disminuye el coste energético del movimiento de datos.

En centros de datos de IA, donde miles de aceleradores trabajan en paralelo, cada mejora incremental tiene impacto multiplicador.

El advanced packaging se convierte en palanca para sostener el crecimiento de la inteligencia artificial.

Chiplets: de tendencia técnica a estrategia industrial

La transición hacia arquitecturas basadas en chiplets ya es visible en fabricantes líderes. El modelo modular facilita:

- Diseños reutilizables.

- Cadena de suministro más flexible.

- Innovación más rápida.

El chip deja de concebirse como unidad indivisible. Evoluciona hacia plataforma componible.

Esta lógica conecta con tendencias más amplias de la industria tecnológica: modularidad, interoperabilidad y especialización.

Más allá del silicio

La integración heterogénea abre la puerta a combinar tecnologías más allá del silicio convencional:

- Fotónica integrada.

- Materiales compuestos.

- Sensores avanzados.

- Componentes 3D apilados.

El encapsulado se convierte en espacio de convergencia tecnológica.

Un cambio de mentalidad

El mensaje transversal del foro es contundente:

La industria vuelve a vivir un momento fundacional. En el pasado, el circuito integrado resolvió una crisis de empaquetado. Hoy, la integración heterogénea y el empaquetado avanzado representan el siguiente salto.

La ventaja competitiva ya no depende exclusivamente del nodo más pequeño. Depende de la arquitectura más inteligente.

Implicaciones estratégicas para Europa

En un contexto geopolítico marcado por la soberanía tecnológica, dominar el advanced packaging adquiere dimensión estratégica.

Como señaló Sung Jin Kim, el packaging avanzado representa una oportunidad real para Europa si desarrolla su propio ecosistema tecnológico. La fabricación avanzada requiere:

- Infraestructura especializada.

- Talento altamente cualificado.

- Ecosistemas colaborativos entre universidades, industria y centros tecnológicos.

Conclusión: el sistema es el nuevo chip

La sesión dedicada a Advanced Packaging and Heterogeneous Integration dejó una idea central :

El futuro de los semiconductores se diseña en la arquitectura del sistema.

Reducir distancia. Aumentar densidad. Integrar funciones. Optimizar coste y energía.

Los chiplets se convierten en sistemas completos. El encapsulado se convierte en plataforma tecnológica.

La próxima década decidirá qué regiones y qué compañías lideran esta transición.

La carrera continúa. Esta vez, en tres dimensiones.

Ver las ponencias de los expertos

Para profundizar en el debate sobre advanced packaging, integración heterogénea, eficiencia energética y el futuro arquitectónico de los chips, puedes ver las ponencias del Future Trends Forum de Semiconductores con:

- Muhannad Bakir, director del 3D Systems Packaging Research Center en Georgia Tech (EE. UU.)

- Sung Jin Kim, director de Tecnología (CTO) de Absolics Inc. (EE. UU.)

- Jekaterina Viktorova, directora ejecutiva y cofundadora de Syenta (Australia)

En los próximos artículos de la serie seguiremos analizando las tendencias clave que definirán la competitividad del sector: desde la arquitectura de interconexión hasta la transición del laboratorio a la fábrica, la inversión estratégica y el desarrollo de talento especializado.

El futuro de los semiconductores se diseña ahora.

Y su impacto alcanzará a toda la economía digital.